30.10.2023

| Version | Content     | Date       | Producer |

|---------|-------------|------------|----------|

| 0       | New Release | 30.10.2023 | DR       |

|         |             |            |          |

|         |             |            |          |

|         |             |            |          |

|         |             |            |          |

|         |             |            |          |

# Contents

| 1 General Description                           | 4  |

|-------------------------------------------------|----|

| 2 Features                                      | 4  |

| 3 Mechanical Specifications                     | 4  |

| 4 Pin Assignment                                | 7  |

| 5 Electrical Characteristics                    | 7  |

| 6 Power On/Off Sequence                         | 12 |

| 7 Pixel Arrangement                             | 14 |

| 8 Optical characteristics                       | 15 |

| 9 Handling, Safety and Environment Requirements | 16 |

| 10 Reliability Test                             | 17 |

| 11 Inspection Standard                          | 20 |

#### 1. General Description

DEE 1120840E5-RGB is a color reflective electrophoretic display module, It has 10.3" active area with 1120 x 840 color pixels (TFT 2240 x 1680), so this display is capable of displaying images at 4096 colors, with integrated circuits including source and gate drivers, can be used in portable electronic devices, such as E-book Reader.

#### 2. Features

- **u** Color Display

- **u** High Contrast Reflective / Electrophoretic Technology

- **u** Wide Viewing Angle

- **u** Ultra Low Power Consumption

- **u** Reflective Mode

- **u** Bistable Display

- **u** Commercial Temperature Range

- u Landscape Mode

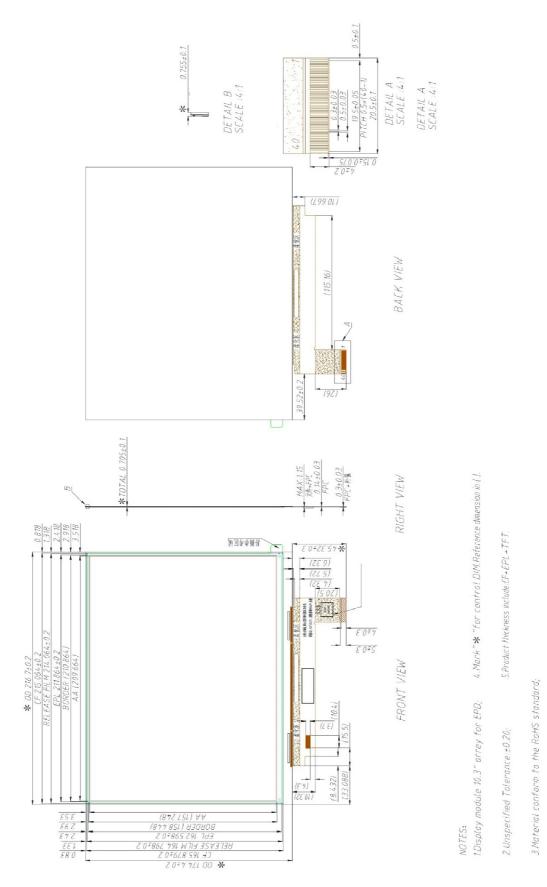

### 3. Mechanical Specifications

#### 3.1 Dimension

| PARAMETER              | VALUE                                   | UNIT | Remark                           |

|------------------------|-----------------------------------------|------|----------------------------------|

| Display Resolution     | 2240 x 1680 (B/W)<br>1120 x 840 (Color) | dots | 271 PPI (B/W)<br>135 PPI (Color) |

| Color                  | 4096                                    | -    | -                                |

| Active Area Dimensions | 209.664 x 157.248                       | mm   | -                                |

| Screen Size            | 10.3                                    | Inch | -                                |

| Pixel Pitch            | 0.0936 x 0.0936                         | mm   | -                                |

| Pixel Configuration    | Square                                  | -    | -                                |

| Overall Dimensions     | 216.70 x 174.40 x 0.705                 | mm   | -                                |

| Weight                 | 70±5                                    | g    | -                                |

## 3.2 Mechanical Drawing of EPD Module

Version: 0

# 4. Pin Assignment

| No. | Pin Name | Description                         |

|-----|----------|-------------------------------------|

| 1   | VGL      | Negative power supply gate driver   |

| 2   | NC       | NO Connection                       |

| 3   | VGH      | Positive power supply gate driver   |

| 4   | NC       | NO Connection                       |

| 5   | VDD      | Digital power supply drivers        |

| 6   | MODE     | Output mode selection gate driver   |

| 7   | CKV      | Clock gate driver                   |

| 8   | SPV      | Start pulse gate driver             |

| 9   | VSS      | Ground                              |

| 10  | VCOM     | Common voltage connection           |

| 11  | VDD      | Digital power supply drivers        |

| 12  | VSS      | Ground                              |

| 13  | CLK      | Clock source driver                 |

| 14  | D0       | Data signal source driver           |

| 15  | D1       | Data signal source driver           |

| 16  | D2       | Data signal source driver           |

| 17  | D3       | Data signal source driver           |

| 18  | D4       | Data signal source driver           |

| 19  | D5       | Data signal source driver           |

| 20  | D6       | Data signal source driver           |

| 21  | D7       | Data signal source driver           |

| 22  | VSS      | Ground                              |

| 23  | D8       | Data signal source driver           |

| 24  | D9       | Data signal source driver           |

| 25  | D10      | Data signal source driver           |

| 26  | D11      | Data signal source driver           |

| 27  | D12      | Data signal source driver           |

| 28  | D13      | Data signal source driver           |

| 29  | D14      | Data signal source driver           |

| 30  | D15      | Data signal source driver           |

| 31  | SPH      | Start pulse source driver           |

| 32  | LE       | Latch enable source driver          |

| 33  | OE       | Output enable source driver         |

| 34  | NC       | NO Connection                       |

| 35  | NC       | NO Connection                       |

| 36  | VPOS     | Positive power supply source driver |

| 37  | NC       | NO Connection                       |

| 38  | VNEG     | Negative power supply source driver |

| 39  | NC       | NO Connection                       |

| 40  | VBORDER  | Border connection                   |

## 5. Electrical Characteristics

#### **5.1 Module DC Characteristics**

| Parameter                            | Symbol | Conditions | Min   | Тур  | Max   | Unit |

|--------------------------------------|--------|------------|-------|------|-------|------|

| Signal Ground                        | VSS    |            | -     | 0    | -     | V    |

| Logic Voltage Supply                 | VDD    |            | 3.0   | 3.3  | 3.6   | V    |

| Logie Voluge Suppry                  | IVDD   | VDD=3.3V   | -     | 4    | 6.5   | mA   |

| Gate Positive Supply                 | VGH    |            | 27    | 28   | 29    | V    |

| Suce i osni ve suppry                | IVGH   | VGH=28V    | -     | 1.1  | 1.2   | mA   |

| Gate Negative Supply                 | VGL    |            | -21   | -20  | -19   | V    |

|                                      | IVGL   | VGL=-20V   | -     | 1    | 13.5  | mA   |

| Source Positive Supply               | VPOS   |            | 14.6  | 15   | 15.4  | V    |

| Source rosarve Suppry                | IPOS   | VPOS=15V   | -     | 1    | 81    | mA   |

|                                      | VNEG   |            | -15.4 | -15  | -14.6 | V    |

| Source Negative Supply               | INEG   | VNEG=-15V  | -     | 0.96 | 81    | mA   |

| Asymmetry Source                     | VASYM  | VPOS+VNEG  | -800  | 0    | 800   | mV   |

| Common Voltage                       | VCOM   | -          | -2.0  | -1.0 | 0.8   | V    |

| Common vonage                        | ICOM   | -          | -     | 0.2  | 0.2   | mA   |

| Standby Power Module                 | PSTBY  | -          | -     | TBD  | TBD   | mW   |

| Typical Power Module                 | РТҮР   | -          | -     | 100  | TBD   | mW   |

| Operating Temperature                | -      | -          | 0     |      | 50    | °C   |

| Storage Temperature                  | -      | -          | -20   | -    | 70    | °C   |

| Maximum Image Update<br>Time at 25°C | -      | -          | -     | 450  | -     | ms   |

Notes:

1. The maximum power and maximum current are specified for the worst case power consumption (Note 5-1).

2. The typical power is measured when "typical images" are displayed (Note 5-2). (Note 5-3).

3. The standby power is the consumed power when the module controller is in standby mode.

4. The listed electrical/optical characteristics are only guaranteed under the controller & waveform provided by DISPLAY.

Note 5-1

The maximum average current and Maximum Currents for B/W display

Note 5-2

The typical power consumption for B/W display

Note 5-3

The typical power consumption at color display

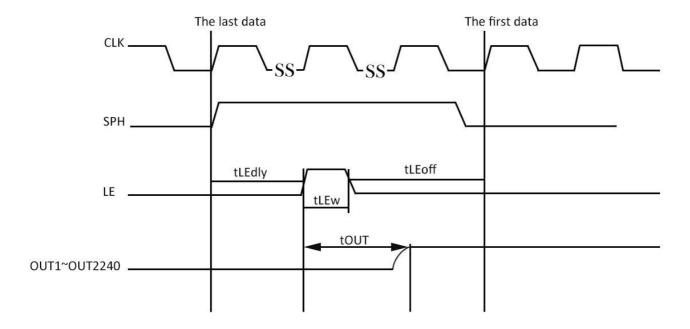

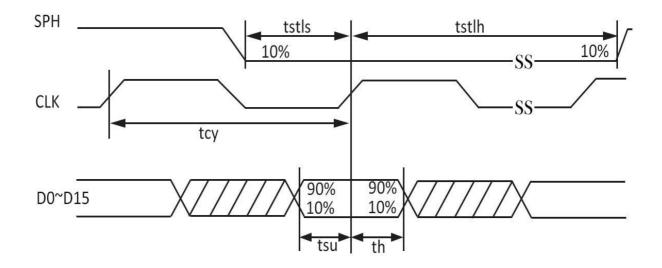

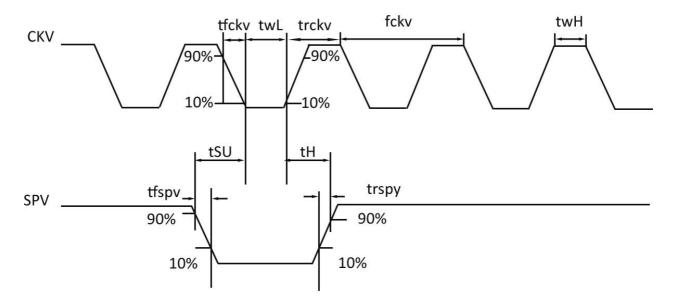

#### **5.2 Module AC characteristics**

| Note: $VDD = 3.0V$ to $3.6V$              | , unless otherwise specified.  |

|-------------------------------------------|--------------------------------|

| 1000.000 = 5.0000000000000000000000000000 | , unless other wise specificu. |

| Parameter                 | Symbol | Min. | Тур. | Max. | Unit | App Pin |  |

|---------------------------|--------|------|------|------|------|---------|--|

| Clock frequency           | fcpv   | -    | -    | 200  | kHz  |         |  |

| Clock CPV high time       | tCPVh  | 0.5  | -    | -    | us   | CPV     |  |

| Clock CPV low time        | tCPV1  | 0.5  | -    | -    | us   |         |  |

| Data setup time           | tSU    | 100  | -    | -    | ns   | CPV     |  |

| Data hold time            | tH     | 300  | -    | -    | ns   | STV     |  |

| Clock CLK cycle time      | tclk   | 40   | -    | -    | ns   |         |  |

| D0 D15, SPH setup time    | tsu    | 8    | -    | -    | ns   |         |  |

| D0 D15, SPH hold time     | th     | 8    | -    | -    | ns   |         |  |

| LE on delay time          | tLEdly | 40   | -    | -    | ns   | Below   |  |

| LE high-level pulse width | tLEw   | 40   | -    | -    | ns   | table   |  |

| LE off delay time         | tLEoff | 40   | -    | -    | ns   |         |  |

| SHR setup time            | tMsu   | 100  | -    | -    | ns   | 15      |  |

| SHR hold time             | tMh    | 10   | -    | -    | ns   |         |  |

|                           |        |      |      |      |      |         |  |

**Output Latch Control Signals**

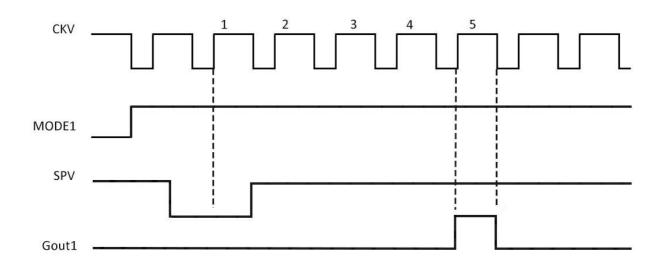

CKV & SPV Timing

#### **Gate Output Timing**

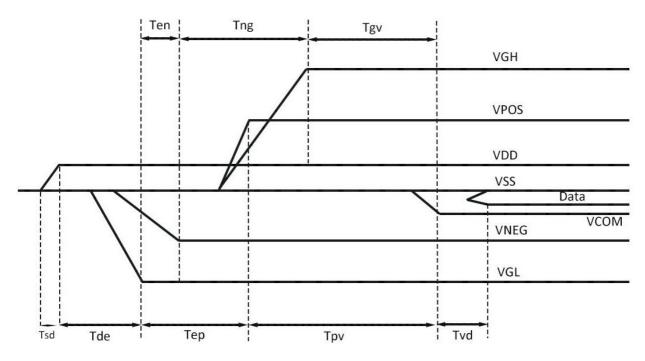

## 6. Power On/Off Sequence

To prevent the device from damage due to latch up, the power on/off sequence shown below must be

followed. When power on: VDD -> VGL -> VNEG/VGH/VPOS ->Vcom

When power off: Vcom -> VNEG/VGH/VPOS -> VGL ->

#### VDD Power on

|     | Min    | Max |

|-----|--------|-----|

| Tsd | 30us   | -   |

| Tde | 100us  | -   |

| Тер | 1000us | -   |

| Tpv | 100us  | -   |

| Tvd | 100us  | -   |

| Ten | Ous    | -   |

| Tng | 1000us | -   |

| Tgv | 100us  | -   |

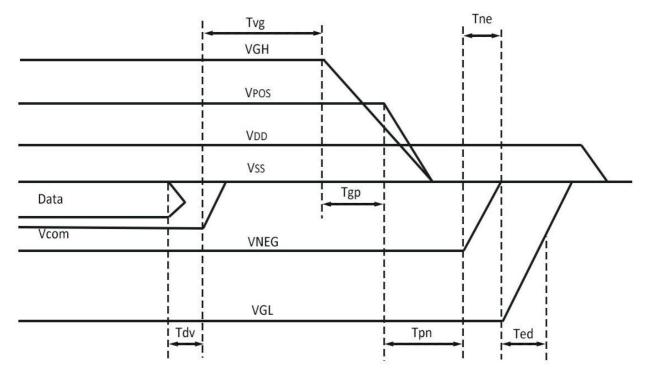

Power Off

|     | Min   | Max |

|-----|-------|-----|

| Tdv | 100us | -   |

| Tvg | Ous   | -   |

| Tgp | Ous   | -   |

| Tpn | Ous   | -   |

| Tne | Ous   | -   |

| Ted | 0.5us | -   |

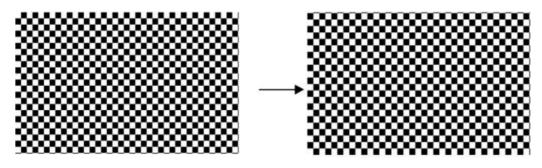

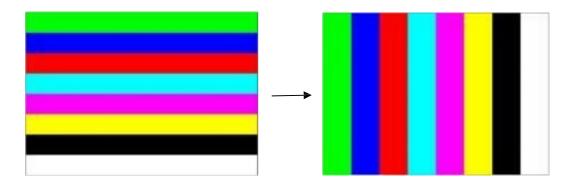

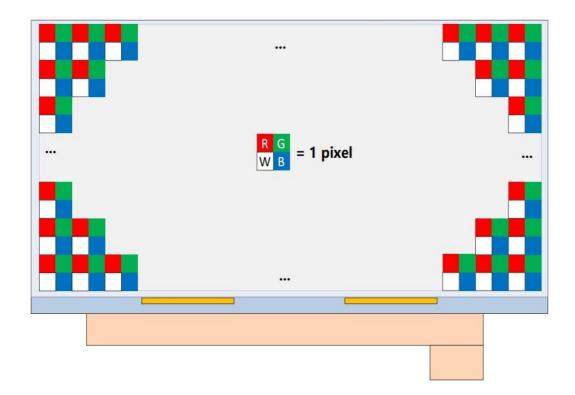

## 7. Pixel Arrangement

The Color EPD module pixel arrangement:

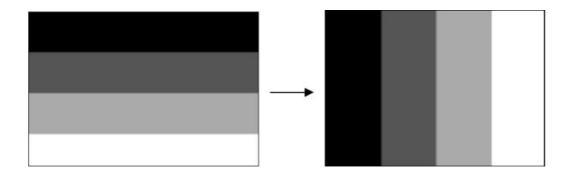

## 8. Optical Characteristics

| Parameter           | Conditions |      | Values |     | Units | Notes  |

|---------------------|------------|------|--------|-----|-------|--------|

| rarameter           | Conditions | Min. | Тур.   | Max | Units | INOLES |

| White Reflectivity  | White      | -    | 20     | -   | %     | 1-1    |

| Contrast Ratio (CR) | -          | -    | 18     | -   | -     | 1-2    |

| NTSC                | -          | -    | ≥5     | -   | %     | -      |

(T= $25^{\circ}$ C, fv = 85Hz. Measurements are made with BYK.)

Notes:

1-1. Luminance meter: BYK.

1-2. CR=Surface Reflectance with all white pixel/Surface Reflectance with all black pixels.

## 9. Handling, Safety and Environment Requirements

## Warning

The display glass may break when it is dropped or bumped on a hard surface. Handle with very high care. Should the display break, do not touch the electrophoretic material. In case of contact with electrophoretic material, wash with water and soap.

### Caution

Disassembling the display module can cause permanent damage and invalidates the warranty agreements.

Observe general precautions that are common to handling delicate electronic components. The glass can break and front surfaces can easily be damaged. Moreover the display is sensitive to static electricity and other rough environmental conditions.

# **10. ReliabilityTest**

| No. | TEST                                                | CONDITION                                                                                                          | METHOD                    | REMARK                                                                                               |

|-----|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|

| 1   | High-<br>Temperature<br>Operation                   | $T = +50^{\circ}C$ , $RH = 30\%$ for 240hrs                                                                        | IEC 60068-2-2Bp           | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 2   | Low-Temperature<br>Operation                        | $T = 0^{\circ}C$ for 240hrs                                                                                        | IEC 60068-2-2Ab           | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 3   | High-<br>Temperature<br>Storage                     | T = +60°C, RH=26% for 168hrs<br>Test in white pattern                                                              | IEC 60068-2-2Bp           | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 4   | Low-Temperature<br>Storage                          | T = -25°C for 240hrs<br>Test in white pattern                                                                      | IEC 60068-2-1Ab           | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 5   | High-<br>Temperature,<br>High-Humidity<br>Operation | $T = +40^{\circ}C$ , $RH = 90\%$ for 168 hrs                                                                       | IEC 60068-2-3CA           | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 6   | High<br>Temperature,<br>High- Humidity<br>Storage   | T = +50°C, RH=80% for240hrs<br>Test in white pattern                                                               | IEC 60068-2-3CA           | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 7   | Thermal Shock                                       | 1 cycle:[-25°C30min]→[+70°C 30<br>min] : 100 cycles<br>Test in white pattern                                       | IEC 60068-2-14            | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 8   | Package<br>Vibration                                | 1.04G, Frequency:10~500Hz<br>Direction: X,Y,Z<br>Duration: 1 hours in each direction                               | Fullpackedfor<br>shipment | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 9   | Package Drop<br>Impact                              | Drop from height of 122 cm<br>on concrete surface.Drop sequence:<br>1 corner, 3edges, 6 faces<br>One drop for each | Fullpacked<br>forshipment | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

| 10  | Electrostatic<br>Effect<br>(non-operating)          | Machine model<br>+/- 250V, 0Ω, 200pF                                                                               | IEC62179<br>IEC 62180     | At the end of the test, electrical,<br>mechanical, and optical<br>specifications shall be satisfied. |

#### 11. Inspection Standard

- 12.1 Appearances Inspection Standard

- 12.1.1 Appearances Specification

This appearance inspection shall be applied to segment EPD modules.

12.1.2 Inspection Conditions

Viewing Angle:  $\alpha = \pm 45^{\circ}$

Viewing Distance: 30cm±10cm

Ambient Luminance: 700~1000 Lux.

Supply Voltage: Typical value described on the Electrical Characteristics

Environment Ambient Temperature: 20°C~25°C

Environment Ambient Humidity: 40~70% RH

ESD should be controlled within  $\pm 200V$

12.1.3 Inspection Level: Level II

Sampling table: GB/T 2828.1-2012 II, unless otherwise agreed in writing.

- 12.1.4 Acceptance Quality Level (AQL) Major Defect: 0.65 , Minor Defect: 1.5

- 12.1.5 Classification of Defects

Defects are classified as either a major or a minor defect defined as below.

Major Defect : It is a defect that is likely to result in failure or to reduce materially the usability of the product for

the intended function.

Minor Defect : It is a defect that will not result in functioning problem with deviation classified.

#### 12.2 Quality Criteria

12.2.1 Zone Definitions

A Zone: EPD Active Area (not including border)

B Zone: Out of Active Area

12.2.2 Appearances Criteria

As shown in the tables below. If any other items, standard values or applicable zones are required to be defined, a written agreement shall be signed, and otherwise a limited sample shall be made for reference.

#### **Major Defects:**

| Item             | Description                                   | Classification |

|------------------|-----------------------------------------------|----------------|

| No Display       | No display shown on screen due to malfunction | Major          |

| Line Missing     | Line missing                                  | Major          |

| Abnormal Display | Unusual pattern or function displayed         | Major          |

| TFT Broken       | TFT broken by external force                  | Major          |

#### **Minor Defects:**

| Item        |                                                                           | Criteria                                                                      | Specific Zone |        |

|-------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------|--------|

| Name        | Description                                                               | Cinena                                                                        | A Zone        | B Zone |

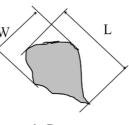

| Dot defect  | Spot/<br>Air bubble/<br>Foreign material in<br>dot shape                  | D≤0.30mm                                                                      | Ignore        | Ignore |

|             |                                                                           | 0.30mm <d≤0.50mm< td=""><td>≤5</td></d≤0.50mm<>                               | ≤5            |        |

|             |                                                                           | D>0.50mm                                                                      | 0             |        |

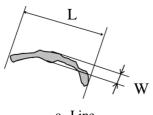

| Line defect | Scratch on top<br>surface/ Foreign<br>material in line or<br>spiral shape | L $\leqslant$ 1.0 mm , W $\leqslant$ 0.15mm                                   | Ignore        | Ignore |

|             |                                                                           | 1.0mm <l≤5.0mm &<br="">0.15mm<w≤0.5mm< td=""><td>≪4</td></w≤0.5mm<></l≤5.0mm> | ≪4            |        |

|             |                                                                           | L>5.0mm or W>0.5mm                                                            | 0             |        |

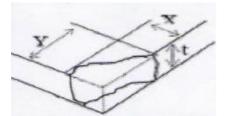

| Chipping    | Corner chip                                                               | Not affect the display, not have diffuse or comminuted cracks                 |               |        |

|             | Edge chip                                                                 |                                                                               |               |        |

| Curl        | Curl for Panel                                                            | $\leq$ 1.0 mm                                                                 |               |        |

#### **Remarks:**

Definitions of "line" and "dot":

a. Line

b. Dot

When L $\leq$ 0.5mm or L $\leq$ 4W, defined as a dot. Definitions of "Chipping":

**PAGE: 19**